Table of Contents

Programmable Logic Devices

$$ AB + AB'C +A'CD + BD $$

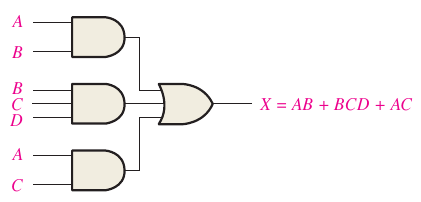

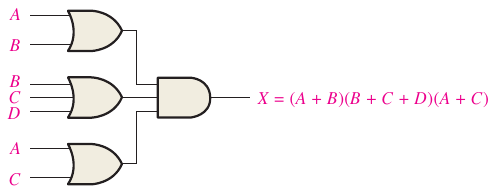

1. Standard forms of Boolean expression

1.1 Sum-of-Products (SOP)

Any Boolean expression can be re-written in terms of SOP.

Check the following conversions.

$$ A(B+CD) = AB + ACD. $$

$$ AB + B(CD + EF) = AB + BCD + BEF $$

$$ (A + B)(B + C + D) = AB + AC + AD + BB + BC + BD $$

$$ ((A + B)' + C)' = (A + B)'' C' = (A + B)C' = AC' + BC' $$

These are Nonstandard SOPs which can be converted to Standard SOPs where each product term has all the variables in the domain (domain is the set of all available variables in an expression).

Convert $AB'C + A'B' + ABC'D$ to standard SOP form.

\begin{equation*} AB'C = AB'C(D+D') = AB'CD + AB'CD'. \\ A'B' = A'B'(C+C') = A'B'C+A'B'C' = (A'B'C+A'B'C')(D+D') \\ = A'B'CD+A'B'CD'+A'B'C'D+A'B'C'D'. \end{equation*}

So the final SOP form is

\begin{equation*} AB'C + A'B' + ABC'D \\ = AB'CD+AB'CD'+A'B'CD+A'B'CD'+A'B'C'D+A'B'C'D'+ABC'D. \end{equation*}

Any product term can be represented using binary numbers.

$$ AB'CD' = 1\cdot 0'\cdot 1\cdot 0' = 1\cdot 1\cdot 1\cdot 1\cdot = 1. $$

This way any product term is equal to 1 only for a unique combination of values for the variables.

1.2 Product-of-Sums (POS)

An example is given above.

Check the following conversion to Standard POS where each sum term has all the variables of the domain. We have to convert $(A+B'+C')(B'+C+D')(A+B'+C'+D)$.

Start by adding a term which has a value of 0. Then apply the rule $(A+B)(A+C)=A+BC$.

$$ A+B'+C' = A+B'+C'+DD' = (A+B'+C+D)(A+B'+C+D'). $$

Finish this.

POS forms also have binary representation. The expression will yield 0 only for one unique combination of values for the variables.

$$ A+B'+C+D' = 0+1'+0+1' = 0+0+0+0 = 0. $$

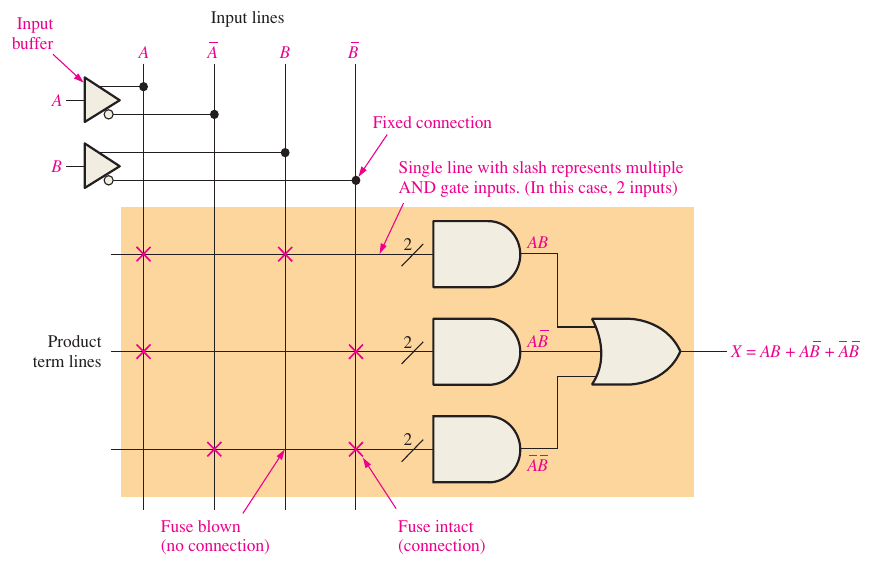

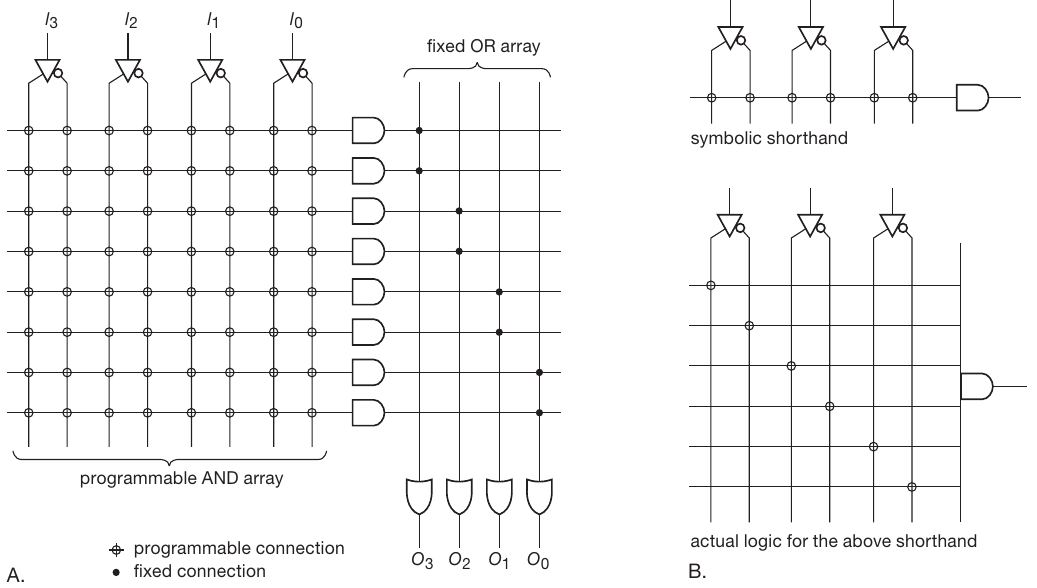

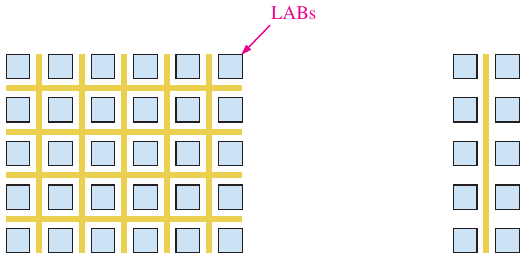

2. Simple PLDs

PAL: programmable array logic, works one time.

GAL: generic array logic, can be re-programmed.

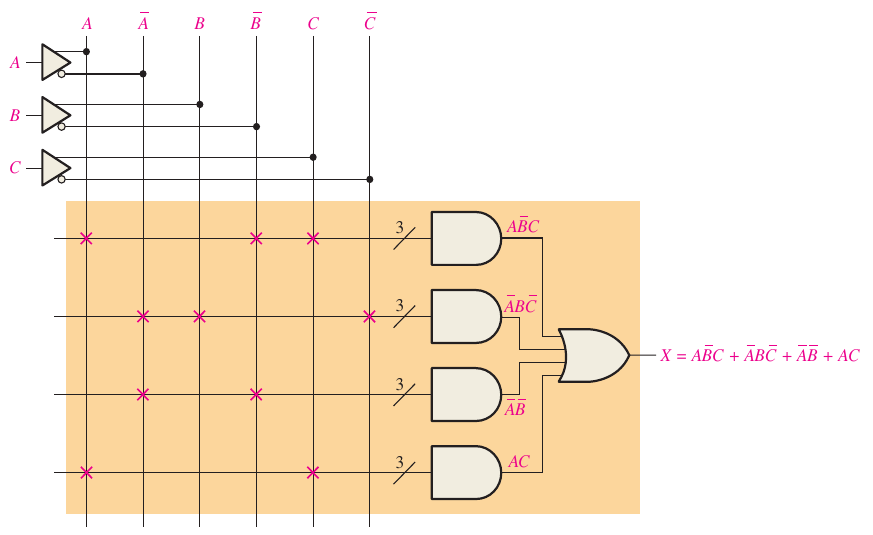

Notations for PAL/GAL:

Example:

The 22V10 PAL:

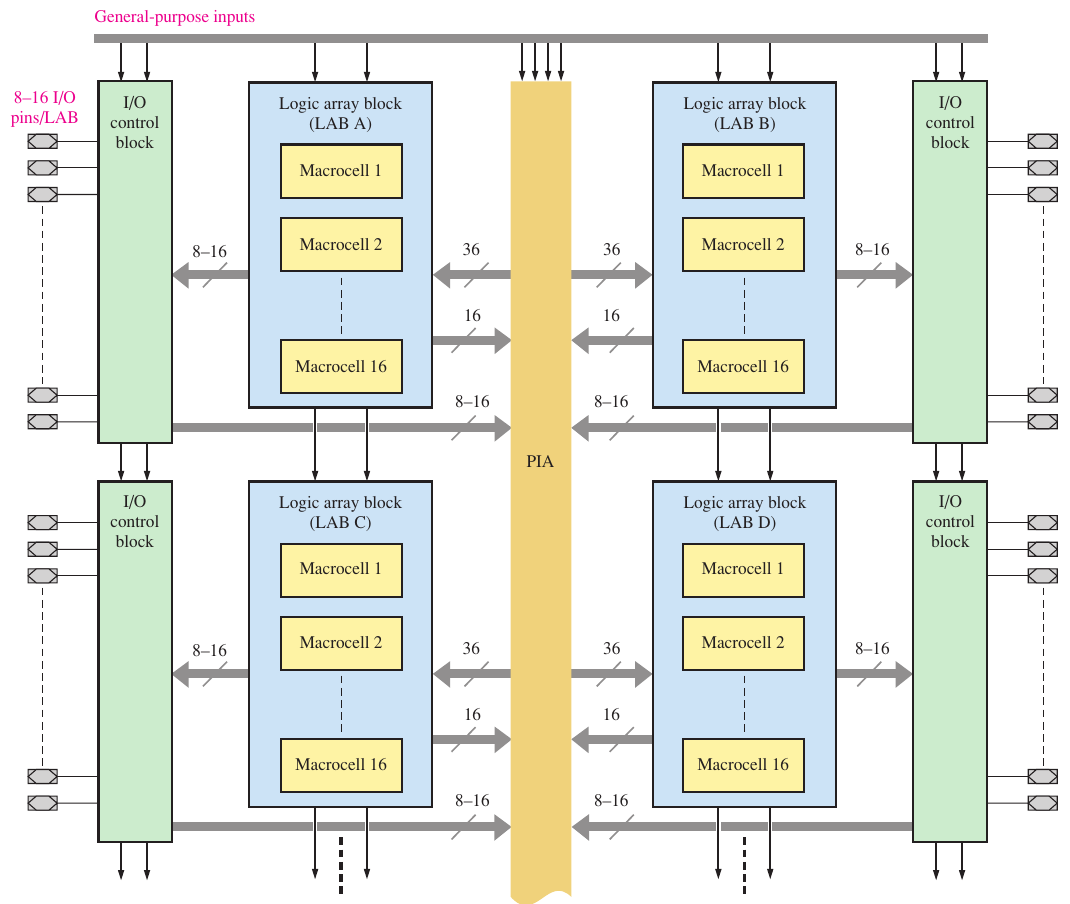

3. Complex PLDs

PIA: programmable interconnect array / AIM: advanced interconnect matrix.

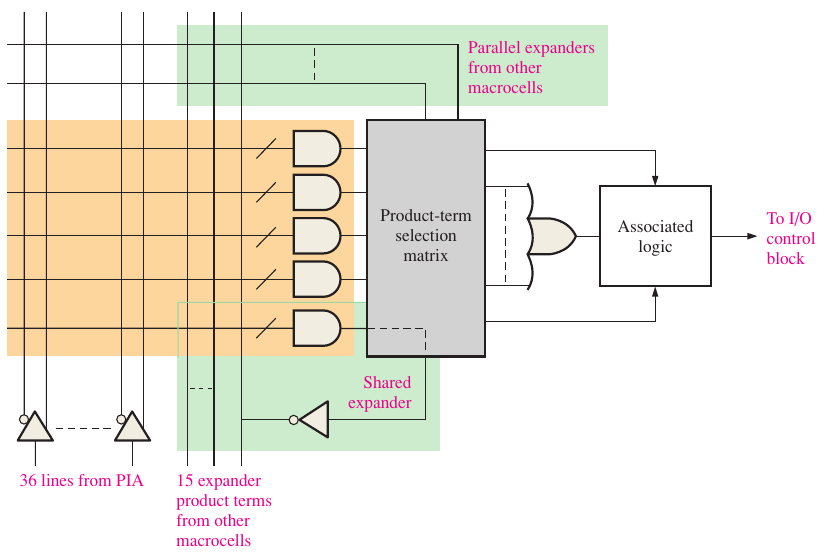

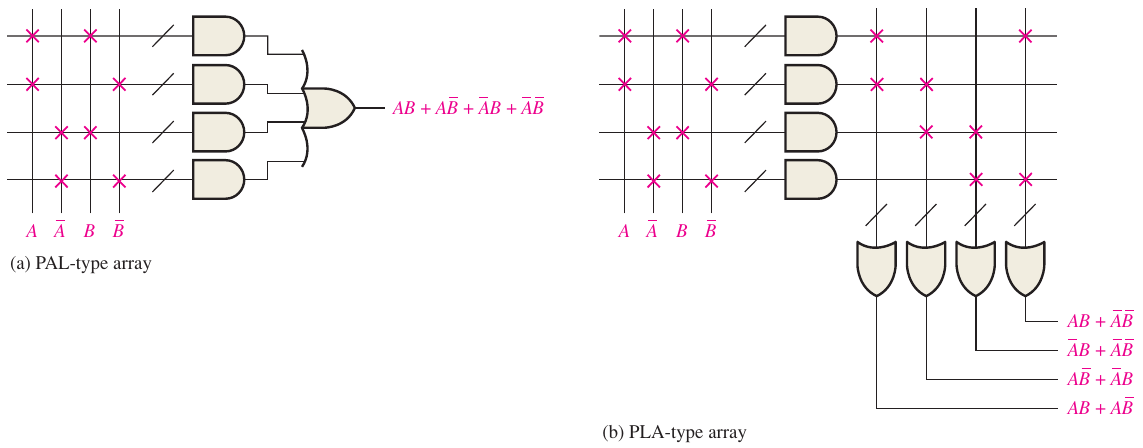

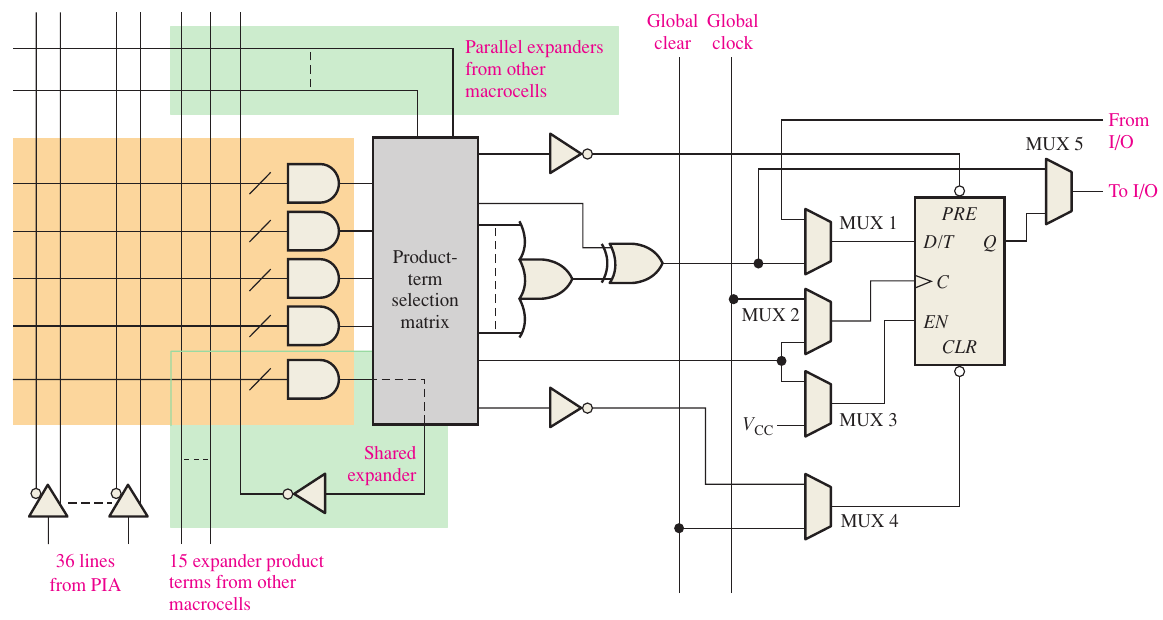

The following is an example of a single macrocell.

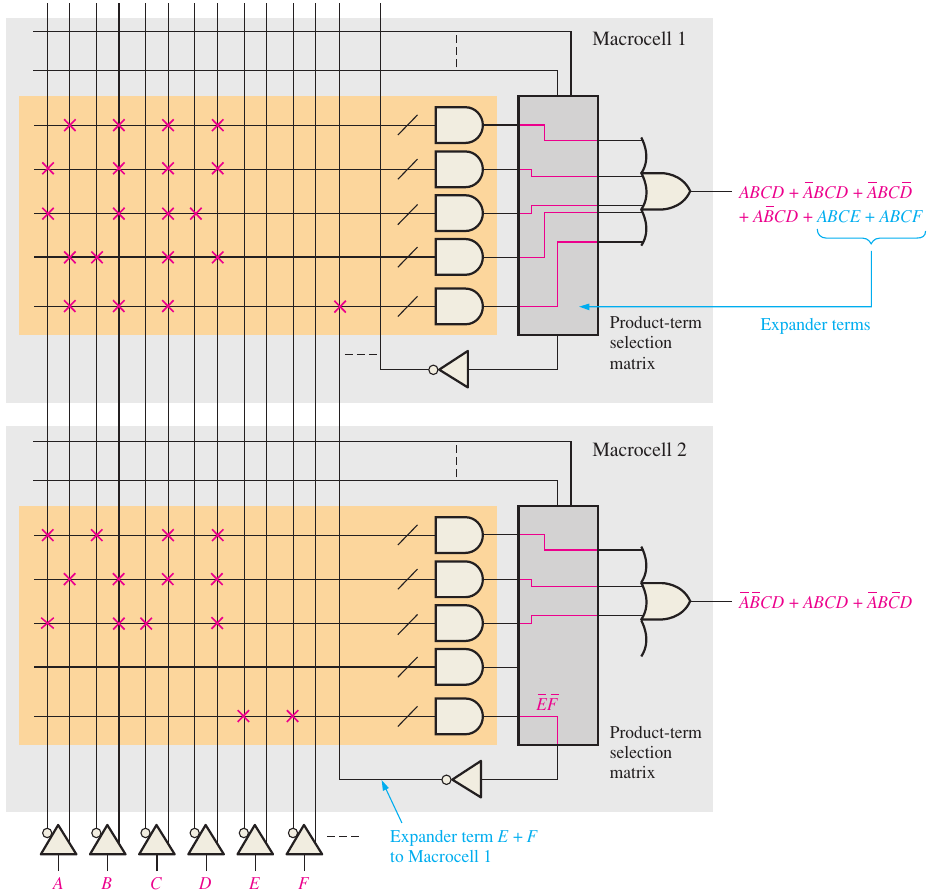

A shared expander can be used to increase the number of product terms in an SOP.

The following is an example of parallel exapnder where the output of one macrocell is fed into the input of another macrocell.

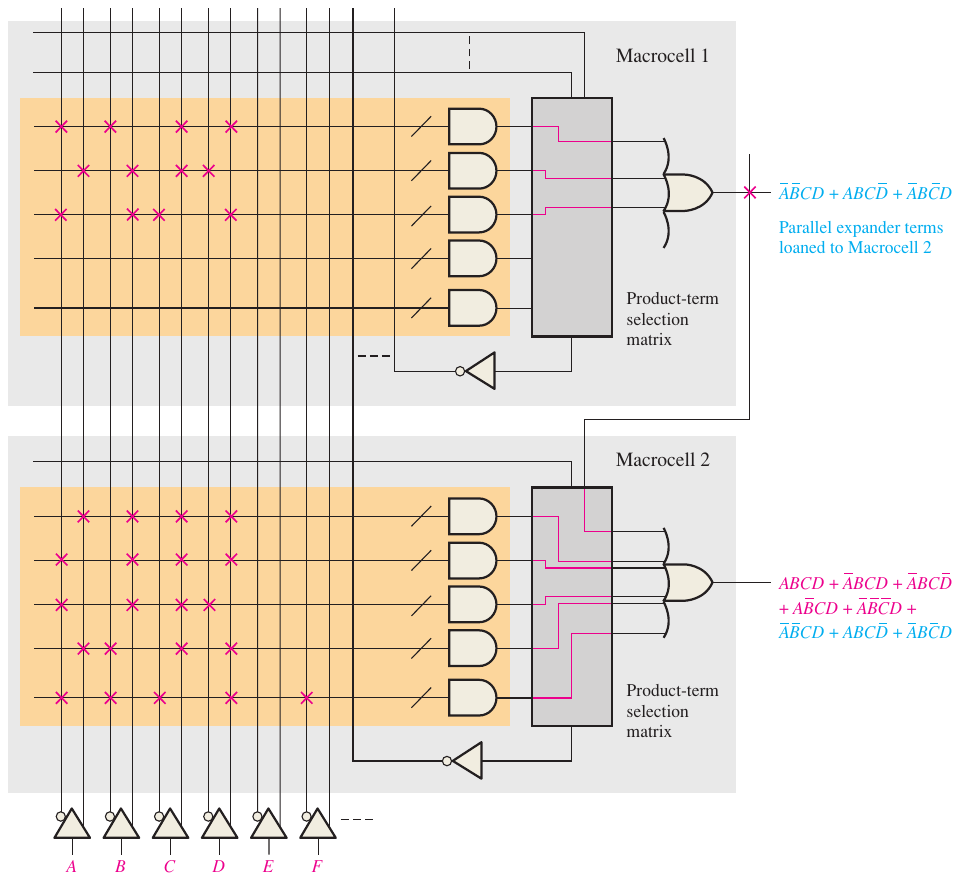

Until now, you have seen the classic architecture. There is also an LUT architecture where LUT stands for lookup table. The architecture is shown below.

Here LABs are arranged in rows and columns and input-output elements (IOE) are in the periphery. The difference between the AND-OR approach and LUT approach is that in the latter case, SOPs are created from LUTs. An LUT is a type of memory.

As shown above, the classic architecture (right panel) uses channels whereas the LUT architecture uses columns and rows.

Altera, Xilinx, Lattice and Atmel make CPLDs. Some example parameters are shown below.

| Number of macrocells | 10–2000 |

| Number of LABs | 10-250 |

| Maximum operating freq. | 20–400 MHz |

| Number of I/Os | 10–1200 |

| DC operating voltage | 1.8, 2.5, 3.3, 5 V |

3.1 Macrocell

A macrocell can be used in combinational or sequential/registered mode.

Carefully check each stage of the above diagram. MUX stands for multiplexer. The XOR gate can be used to complement the SOP form to produce POS form.

In combinational mode, only MUX 5 is used.

In registered mode, MUX 1, 2, 3 and 5 are used together.

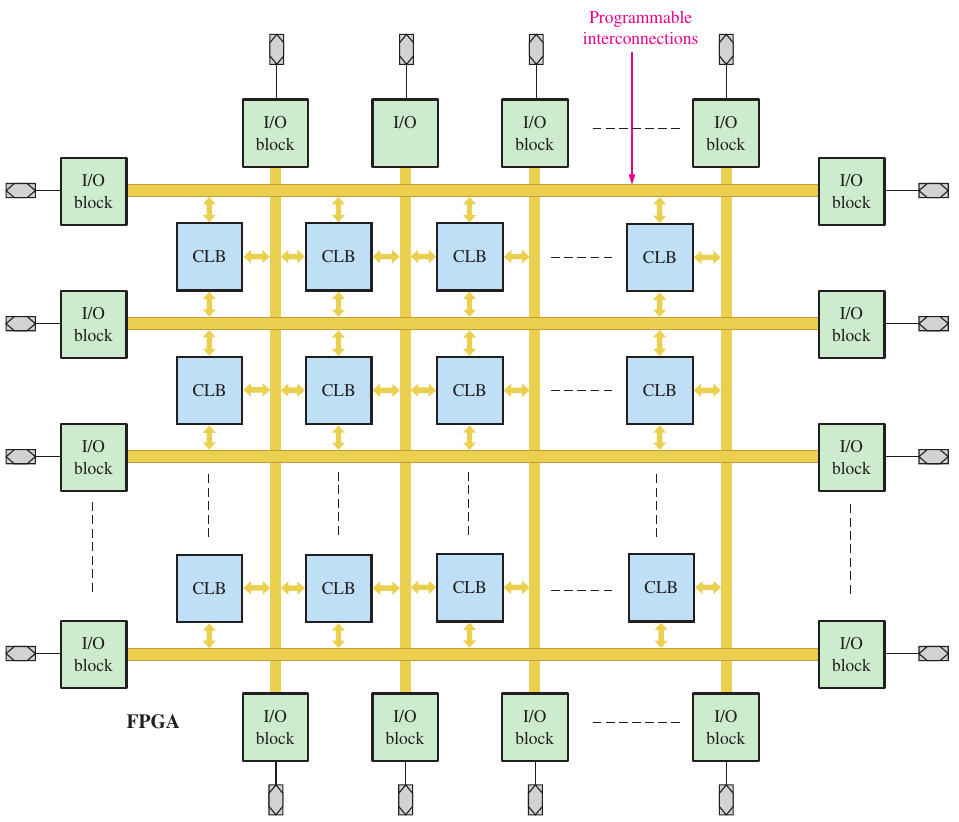

4. FPGAs

Field-programmable gate arrays.

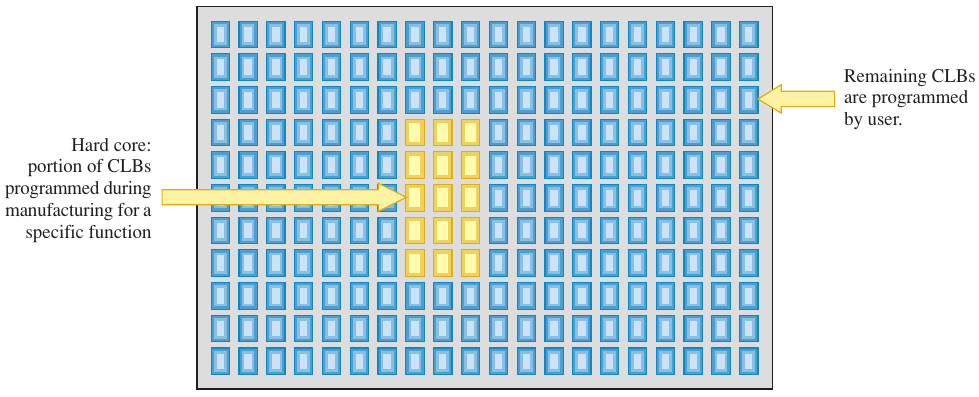

I/O blocks, configurable logic blocks (CLB) and programmable interconnections make an FPGA.

If the CLBs are much simpler than the LABs or macrocells of CPLDs, the FPGA is called fine grained. If the CLBs are more complex, they are called coarse grained.

FPGAs are reprogrammable and the programming is done via SRAM (static RAM).

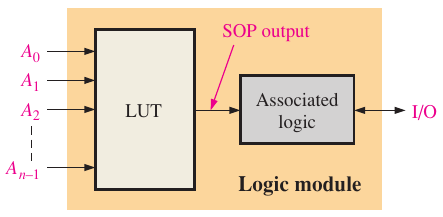

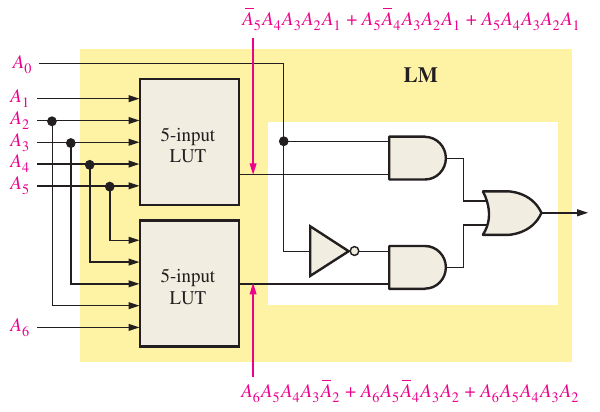

A CLB has multiple logic module (LM); such a module is shown below.

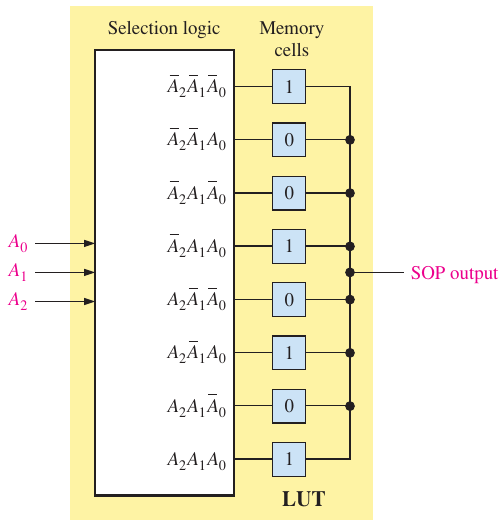

And the operation of a LUT is shown below.

With 3 inputs, you can create an SOP with 8 terms. If a memory cell has 1, the SOP term associated with it will appear in the final expression.

An LM can have multiple LUTs producing multiple SOPs. The LUTs can share inputs. This is the normal mode. In the extended mode two LUTs can share inputs to allow more variables in the SOP as shown below.

Volatile (all memory lost at power down) FPGAs might have nonvolatile configuration memory or host processors to reconfigure the CLBs at power up.

A reprogrammable FPGA can have non-reprogrammable hard core, or slightly reprogrammable soft core. These cores are called intellectual property (IP).